Sistemele de calcul bazate pe microprocesoare sau microcontrolere se numesc microsisteme digitale. Exista 2 tipuri de echipamente care sunt microsisteme digitale: microcalculatoarele si sistemele de calcul orientate pe aplicatii.

Microprocesorul se poate defini ca fiind un circuit logic programabil de catre utilizator, intr-o singura capsula si cu functie de procesor de uz general.

Microcontrolerul se poate defini ca un circuit logic, programabil de catre utilizator, cu o structura adaptata pentru rezolvarea unei largi game de aplicatii de timp real. El nu este folosit ca procesor de uz general ci ca procesor orientat pe aplicatii, fiind, in general, inclus in echipamentul pe care il conduce.

DSP - prelucreaza digital semnale analogice

UAL - unitate aritmetica si logica

DCC - disp de comanda si control

DCI - decodificator de instructiuni

(comanda DCC)

RI - registru de instructiuni (le

memoreaza temporar)

PC - numara adresele

TD - tampon de date

TA - tampon de adrese

REG - registre (capacitate mica)

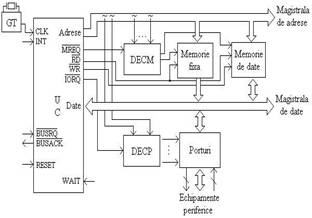

UC - up/uc + generator de tact, amplif/

UC - up/uc + generator de tact, amplif/

demux mag.

Mem. Fixa - ROM, OTP, EPROM,

EEPROM, Flash

Mem. Scr/cit - (S/D)RAM - mem. temp.

Porturi - interfata dintre UC si I/O

DECM - gen semnale selectie pt mem

DECP - decodif. porturile

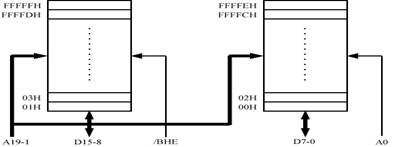

/BHE - Bus High Enable (octet superior D15-D8)

/RD - Read (se face o operatie de citire I/O)

READY - s-a incheiat o operatie de transfer a datelor

INTR - Interrupt Request (se intra in rutina de tratare a intreruperii; poate fi mascata)

NMI - Non-Maskable

Interrupt (intrerupere ce nu poate fi mascata)

RESET - se intrerupe imediat activitatea up

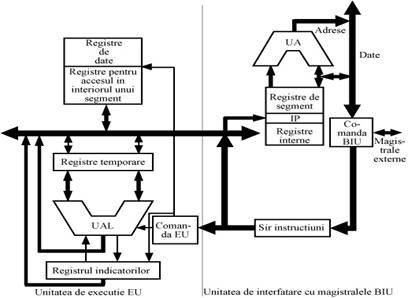

EU executa toate instructiunile, furnizeaza date si adrese pentru BIU.

BIU aduce instructiuni, citeste operanzi si scrie rezultate.

capacitatea de memorie direct adresabila este de 1 MO,

memoria este gestionata in segmente:

i. avantaje:

este facilitata programarea modulara; fiecare modul poate ocupa unul sau mai multe segmente putand fi dezvoltat independent unul fata de celalalt;

faciliteaza relocarea dinamica a programelor; pentru aceasta este necesar ca acestea sa nu afecteze continuturile registrelor segment si sa nu faca referire la locatii din afara segmentului; programul poate fi plasat oriunde in memorie prin modificarea continuturilor registrelor de segment;

se poate utiliza un numar mare de stive, prin plasarea adresei de inceput a segmentului stiva in registrul SS si a varfului stivei in SP;

ii. dezavantaje:

limitari in lungimea programelor introduse de dimensiunile segmentelor;

adresa fizica se obtine din doua configuratii printr-un mecanism care necesita timp deci duce la o scadere a vitezei de lucru.

Organizarea memoriei:

00000H - 00013H - zona dedicata,

00014H - 0007FH - zona rezervata,

00080H - FFFEFH - zona disponibila,

FFFF0H - FFFFBH - zona dedicata,

FFFFCH - FFFFFH - zona rezervata.

Comanda memoriei

Sistemul de intrare/ iesire

conectarea porturilor in spatiul de memorie,

conectarea porturilor in spatiul de intrare/ iesire dedicat: suprapus peste primul segment de memorie.

Transfer de operanzi pe:

16 biti,

8 biti pe D0-7 (adresa para de port) sau D8 - 15 (adresa impara de port).

Adrese de port pe:

16 biti: se foloseste adresarea indirecta prin DX (65536 porturi),

8 biti: se foloseste adresarea directa (256 porturi).

Instructiuni IN si OUT

transfer port - registrul AX (16 biti) sau AL, respectiv AH (8 biti).

Sistemul de intreruperi

intreruperi externe si interne,

256 intreruperi, accesul la rutina de tratare este vectorizat.

Tabela vectorilor de intrerupere: primii 1024 octeti:

|

Tip |

Intrare |

Adresa |

|

Eroare la divizare |

00000H |

|

|

Pas cu pas |

00004H |

|

|

Intrerupere nemascabila |

00008H |

|

|

Breakpoint |

0000CH |

|

|

Rezervat |

00010H |

|

|

Depasire |

00014H - 0007CH |

|

|

Disponibil |

00080H - 003FCH |

|

|

Instructiuni |

00000H - 003FCH |

cicluri normale cicluri cu generare in avans a adreselor

(cistig: minimizarea numarului de stari de asteptare)

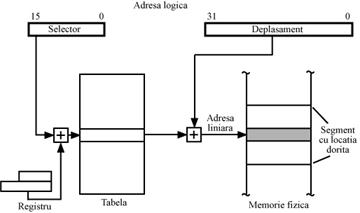

Adresa logica = Deplasament + Registru selector;

Adresa logica = Deplasament + Registru selector;

Deplasament: 32 biti, furnizat de instructiune;

Registru selector = Registru de segment;

Continutul registrului selector: index in Tabela;

O intrare in Tabel = grup de 8 octeti numit descriptor;

n Dezavantaj al mecanismului de segmentare:

q citirea unui descriptor adica 2 cicluri suplimentare; solutia:

q Registre cache pentru descriptori.

n Avantaje ale mecanismului de segmentare:

q faciliteaza implementarea sistemelor multitasking prin asignarea segmentelor de cod si date propri,

q facilitatile de protectie oferite de microprocesor asigura separarea segmentelor corespunzatoare unui task de cele corespunzatoare altui task si de cele corespunzatoare sistemului de operare; in acest fel pot rula concurent mai multe taskuri, izolate unul de celalalt, fiecare avand acces doar la propriile resurse si izolate de resursele sistemului de operare,

q un program oarecare nu poate modifica resursele sistemului de operare si o eroare dintr-un program nu poate afecta decat propriile resurse,

q in cazul existentei unei erori intr-un program care duce la abandonarea sa, alte programe pot rula pentru a diagnostica si, eventual corecta, eroarea.

Fiecarui task ii corespunde un segment special, numit Segment Stare Task, TSS, care contine toate informatiile necesare actualizarii starii microprocesorului si revenirii in taskul de unde s-a facut comutarea.

- mecanismul de paginare preia adresa generata de cel de

segmentare, adresa liniara, si o transforma in adresa

fizica;

- mecanismul de paginare preia adresa generata de cel de

segmentare, adresa liniara, si o transforma in adresa

fizica;

- daca mecanismul de paginare nu este activat, atunci adresa liniara devine adresa fizica;

n Avantaje:

q se pot gestiona 1024 x 1024 = 1 M pagini a cite 4 Ko;

q tabelele sunt ele insele pagini de cite 4 Ko;

q cere zone de memorie contigue de dimensiuni mici: 4 Ko fata de un mecanism pe un singur nivel, cu pagini de 4 Ko, pentru care ar fi fost necesara o tabela cu 1 M intrari si considerand 4 octeti/ intrare ar fi fost necesara o zona de memorie contigua de 4 Mo.

n Dezavantaje:

q necesitatea executiei a doua accese suplimentare la memorie pentru fiecare acces dorit, ceea ce inseamna timp suplimentar;

q solutia: prevederea in microprocesor a unei memorii cache pentru paginare, cunoscuta sub denumirea de TLB;

q contine adresele celor mai recent folosite 32 pagini;

q tabela are 32 intrari si poate acoperi 128 Ko de memorie.

|

Amplificarea liniilor unidirectionale Amplificarea liniilor bidirectionale

Cu facilitatea de cedare a magistralelor

Demultiplexarea centrala Demultiplexarea locala

|

|

Solutia seriala

Solutia paralela

Solutia rotativa:

- similara cu cea paralela doar ca prioritatea este reasignata in mod dinamic;

- codificatorul cu prioritate este inlocuit de un circuit mai complex care roteste prioritatea intre arbitri care cer acces, asigurand astfel fiecarui arbitru timp egal pe magistrala.

Circuitul 8289 actioneaza asupra circuitului 8288 (controler de magistrala):

- cand arbitrul permite accesul procesorului la magistrala comuna, el va activa linia /AEN; aceasta va permite accesul separatoarelor de pe liniile de adrese si date pe magistrala comuna; semnalele de comanda vor fi generate, de catre circuitul 8288, in functie de tipul de ciclu executat de procesor;

- cind arbitrul nu permite accesul procesorului la magistrala comuna, el va dezactiva semnalul /AEN; circuitul 8288 va trece toate semnalele de comanda a transferurilor cu resursele de pe magistrala comuna in starea lor inactiva, separatoarele de pe liniile de date si adrese intre magistralele procesorului si magistrala comuna vor fi trecute in a 3-a stare permitand astfel accesul altor procesoare la magistrala comuna.

Microprocesorul este introdus in stari de WAIT;

Intr-un sistem multimaster este necesara definirea unei prioritati la existenta cererilor de acces simultane la magistrala comuna; 3 tehnici: paralela, seriala si rotativa.

n Proiectarea unui decodificator de memorii

q rolul unui decodificator de memorii este sa genereze semnale de selectie pentru circuitele de memorie din microsistem;

q pozitia pe care o ocupa, in cadrul microsistemului, este intre unitatea centrala si circuitele de memorie;

q proiectantul porneste de la asa numita harta a memoriei care arata plasarea circuitelor de memorie in spatiul de adresare directa a microprocesorului;

q plasarea se face in functie de capacitatea fiecarui circuit, de cerintele aplicatiei, ale unitatii centrale si ale sistemului de operare, daca exista

q aplicatia va fixa capacitatea totala de memorie necesara

q in functie de capacitatea circuitelor de memorie disponibile, va rezulta si numarul de circuite necesare

q capacitatea fiecarui circuit va determina dimensiunea zonei ocupate de respectivul circuit.

Intrarile decodificatorului de memorii:

q linii din magistrala de adrese, corespunzatoare zonelor ocupate de aceste circuite si

q semnale de comanda (uneori).

Decodificarea completa:

se construieste un tabel avand ca si coloane rangurile de adrese si ca linii configuratii care arata adresa de inceput si de sfarsit a fiecarei zone ocupate de cate un circuit;

pentru fiecare circuit, se inspecteaza coloanele, pornind de la rangurile mai semnificative spre cele mai putin semnificative si se stabilesc acele ranguri ce raman nemodificate oricare ar fi locatia adresata in respectiva zona

o functie combinationala a acestor intrari va individualiza zona respectiva si va constitui ecuatia pentru semnalul de selectie a circuitului care o acopera

exemplu: sa se proiecteze decodificatorul pentru urmatoarea harta a memoriei:

i. 0000H - 1FFFFH - circuitul de memorie C1, avand capacitatea de 64K x 16 biti

ii. H - FFFFH - circuitul de memorie C2, avand capacitatea de 32K x 16 biti,

iii. H - FFFFH - circuitul de memorie C3, avand capacitatea de 32K x 16 biti.

Tabelul:

|

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A9 |

A8 |

A7 |

A6 |

A5 |

A4 |

A3 |

A2 |

A1 |

C |

|

C1 |

|||||||||||||||||||

|

|

C2 |

||||||||||||||||||

|

C3 |

|||||||||||||||||||

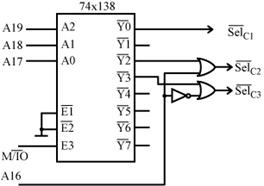

n Ecuatiile semnalelor de selectie:

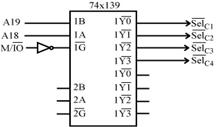

q /SELC1 = /A19 * /A18 * /A17

q /SELC = /A19 * A18 * /A17 * /A16

q /SELC = /A19 * A18 * A17 * A16

n Schema decodificatorului

n Decodificarea incompleta:

q se construieste tabelul ca in cazul anterior dar functia sau functiile care vor genera semnalele de selectie nu vor utiliza toate liniile de adresa ce raman nemodificate oricare ar fi locatia adresata din zona respectiva

q aceasta va duce la o simplificare a decodificatorului dar un acelasi circuit, sau diviziune, va ocupa mai multe zone de memorie de aceeasi capacitate ca cea a circuitului

q daca nu se considera o linie de adresa un acelasi circuit va ocupa 2 zone de memorie, daca nu se considera 2 linii de adresa un acelasi circuit va ocupa 4 zone de memorie s. a. m. d.

q exemplu: sa se proiecteze decodificatorul pentru urmatoarea harta a memoriei:

n 0000H - 0FFFFH - circuitul de memorie C1, avand capacitatea de 32K x 16 biti

n H - FFFFH - circuitul de memorie C2, avand capacitatea de 32K x 16 biti,

n H - FFFFH - circuitul de memorie C3, avand capacitatea de 32K x 16 biti,

n C H - CFFFFH - circuitul de memorie C , avand capacitatea de 32K x 16 biti.

q Tabelul:

|

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A9 |

A8 |

A7 |

A6 |

A5 |

A4 |

A3 |

A2 |

A1 |

C |

|

C1 |

|||||||||||||||||||

|

C2 |

|||||||||||||||||||

|

C3 |

|||||||||||||||||||

|

C4 |

|||||||||||||||||||

n Ecuatiile semnalelor de selectie in cazul decodificarii incomplete:

q /SELC1 = /A19 * /A18

q /SELC = /A19 * A18

q /SELC = A19 A18

q SELC4 = A19 * A18

n Fiecare circuit ocupa 4 zone de memorie, avind capacitati egale cu cele ale circuitului; de exemplu circuitul C1 ocupa zonele:

q 00000H - 0FFFFH,

q 10000H - 1FFFFH,

q 20000H - 2FFFFH si

q 30000H - 3FFFFH.

Schema decodificatorului in cazul decodificarii incomplete

|

Politica de confidentialitate |

| Copyright ©

2025 - Toate drepturile rezervate. Toate documentele au caracter informativ cu scop educational. |

Personaje din literatura |

| Baltagul caracterizarea personajelor |

| Caracterizare Alexandru Lapusneanul |

| Caracterizarea lui Gavilescu |

| Caracterizarea personajelor negative din basmul |

Tehnica si mecanica |

| Cuplaje - definitii. notatii. exemple. repere istorice. |

| Actionare macara |

| Reprezentarea si cotarea filetelor |

Geografie |

| Turismul pe terra |

| Vulcanii Și mediul |

| Padurile pe terra si industrializarea lemnului |

| Termeni si conditii |

| Contact |

| Creeaza si tu |