Consideratii teoretice referitoare la logica cuplata in surse

Performantele circuitelor cu logica cuplata in sursa pot fi descrise tinand cont de urmatorii parametri fundamentali:

Excursia

tensiunii (tensiunea de swing) - ![]()

Curentul de

polarizare (bias current)- ![]() ;

;

geometria

tranzistoarelor- ![]() ;

;

intarzierea (delay).

Acesti patru parametri sunt inter-dependenti. Un exemplu concret il constituie dependenta intarzierii fata de ceilalti trei parametri; ea poate fi teoretic micsorata daca utilizam o rezistenta de iesire de valoare mai mica. De asemenea, intarzierea e proportionala si cu latimea tranzistoarelor.

Excursia tensiunii este direct proportionala cu curentul:

![]() (3)

(3)

Buffer/ Inversor

Poarta de baza a circuitelor SCL o constituie Buferul/Inversor. Aceasta este totodata si buffer si inversor, datorita naturii diferentiale caracteristica a circuitelor cu logica cuplata in sursa. [1]

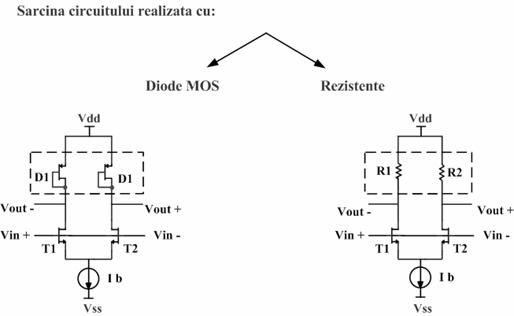

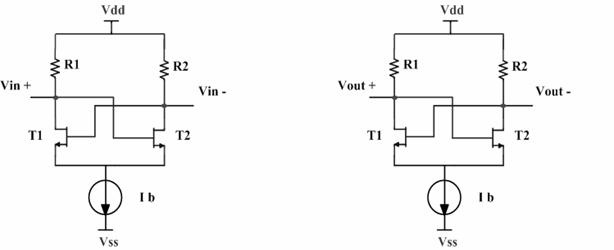

Schema

este prezentata in figura 12. Se poate folosi o oglinda de curent (formata din

tranzistoare) pentru a asigura o sursa constanta de curent, ![]() . Tranzistoarele T1 si T2 formeaza perechea diferentiala, iar

sarcina circuitului o reprezinta diodele D1 si D2 in primul circuit din figura

si rezistentele R1 si R2, in al doilea circuit. Dupa cum am amintit si

anterior, Bufferul/Inversor este singura poarta logica care are un singur set

de intrari diferentiale.

. Tranzistoarele T1 si T2 formeaza perechea diferentiala, iar

sarcina circuitului o reprezinta diodele D1 si D2 in primul circuit din figura

si rezistentele R1 si R2, in al doilea circuit. Dupa cum am amintit si

anterior, Bufferul/Inversor este singura poarta logica care are un singur set

de intrari diferentiale.

In

figura este evidentiata functia de Buffer, iar ca elemente de sarcina, am

utilizat in primul circuit doua diode, respectiv doua rezistente in al doilea. Daca

se va inversa ![]() cu

cu ![]() circuitul va actiona ca un inversor, opusul bufferului.

circuitul va actiona ca un inversor, opusul bufferului.

Figura 12. Bufferl/Inversor al familiei SCL

Pentru a putea determina

tensiunea de iesire a portii trebuie in primul rand analizat curentul de drena

a tranzistoarelor din perechea diferentiala. Intrarea diferentiala a perechii

se va defini prin urmatoarea relatie: ![]() (4)

(4)

Curentul prin tranzistorul T1 este:

(5), unde:

(5), unde:

![]() este curentul de

polarizare;

este curentul de

polarizare;

W, L reprezinta latimea, respectiv, lungimea tranzistoarelor;

![]() si

si ![]() sunt parametrii

tranzistoarelor,

sunt parametrii

tranzistoarelor, ![]() reprezinta mobilitatea

electronilor si

reprezinta mobilitatea

electronilor si ![]() este capacitate a

portii si poate fi exprimata ca si raportul dintre permitivitate

este capacitate a

portii si poate fi exprimata ca si raportul dintre permitivitate ![]() si grosimea stratului

de oxid a portii (gate) tranzistorului -

si grosimea stratului

de oxid a portii (gate) tranzistorului - ![]() .

.

Ecuatia de mai sus este valabila doar cand curentul este comutat

in perechea diferentiala. Odata ce acest curent trece prin tranzistorul T1 sau

T2, relatia nu mai este valabila, si este inlocuita de  (6), relatie descrisa

in figura de mai jos, definita de domeniul

(6), relatie descrisa

in figura de mai jos, definita de domeniul ![]() (7) .

(7) .

Figura

13. Relatia dintre ![]() si

si ![]()

![]() reprezinta tensiunea

de intrare diferentiala atunci cand curentul trece prin T1, iar

reprezinta tensiunea

de intrare diferentiala atunci cand curentul trece prin T1, iar ![]() , tensiunea de intrare

diferentiala cand curentul trece prin T2.

, tensiunea de intrare

diferentiala cand curentul trece prin T2.

Tensiunile de iesire vor fi ![]() si

si ![]() :

:

![]() (8)

(8)

Dupa cum se observa si in

figura 13, cand valoarea tensiunii ![]() este zero, curentul

prin tranzistorul T1 este

este zero, curentul

prin tranzistorul T1 este ![]() , rezulta ca si prin tranzistorul T2 avem aveasi valoare.

, rezulta ca si prin tranzistorul T2 avem aveasi valoare.

Aceste relatii indica

valorile tensiunilor de iesire ![]() si

si ![]() ca fiind numeric egale.

ca fiind numeric egale.

Buffer/Inversor este cea mai simpla poarta logica implementata in logica SCL, insa demonstreaza importanta perechii diferentiale. In afara de acesta, circuite comune in logica cu surse cuplate sunt: portile Si/Si-Nu, Sau/Sau-Nu, XOR, circuitele Flip-Flop, Divizor cu 4; in continuare se vor analiza aceste porti care, spre deosebire de Buffer/Inversor, contin mai multe perechi diferentiale de tranzistoare.

Se vor urma pasii descrisi in continuare pentru determinarea tensiunii de iesire:

Pasul 1. Calcularea tensiunii de swing ![]() si a castigului

si a castigului

Prima oara trebuie sa determinam limitele domeniului tensiunii acceptate. Pentru aceasta, consideram ca tranzistoarele de la intrare lucreaza in regim saturat chiar si atunci cand este prezenta amplitudinea maxima a semnalului. Conditia ca tranzistoarele sa lucreze in regim saturat este :

![]() (9)

(9)

Cazul cel mai defavorabil il prezinta situatia in care tensiunea drena-sursa si poarta-sursa a tranzistoarelor de intrare este:

(10)

(10)

Unde,![]() si

si ![]() sunt intrarile si

iesirile in regim static,

sunt intrarile si

iesirile in regim static, ![]() si

si ![]() sunt intrarile si iesirile tensiunii de swing,

sunt intrarile si iesirile tensiunii de swing, ![]() este tensiunea de prag a tranzistoarelor NMOS, iar potentialul sursei tranzistoarelor de

intrare se va considera constant. Utilizand relatiile 9 si 10, rezulta:

este tensiunea de prag a tranzistoarelor NMOS, iar potentialul sursei tranzistoarelor de

intrare se va considera constant. Utilizand relatiile 9 si 10, rezulta:

![]() (11)

(11)

Daca consideram ![]() si castigul

si castigul ![]() , rezulta:

, rezulta:

![]() (12)

(12)

Pentru o buna functionalitate in cascada a

circuitelor, se va utiliza valoare lui ![]() egala cu 1. In acest caz, excursia tensiunii de la intrare

este egala cu excursia tensiunii de la iesire, iar valoarea ei trebuie sa fie

mai mica decat cazul cel mai defavorabil a tensiunii de prag a tranzistoarelor

NMOS.

egala cu 1. In acest caz, excursia tensiunii de la intrare

este egala cu excursia tensiunii de la iesire, iar valoarea ei trebuie sa fie

mai mica decat cazul cel mai defavorabil a tensiunii de prag a tranzistoarelor

NMOS.

Pasul 2. Dependenta timpului de intarziere de excursia tensiunii

Pentru a demonstra aceasta dependenta se va

presupune ca rezistenta echivalenta de iesire conectatat in paralel cu suma

capacitatilor parazite conectate la nodurile de iesire - ![]() , primeste un curent care poate varia intre 0 si

, primeste un curent care poate varia intre 0 si ![]() .

.

(13)

(13)

Timpul de intarziere (time delay) va fi definit

in momentul cand tensiunea de iesire va atinge valoarea ![]() , de relatia 14:

, de relatia 14:

(14)

(14)

Rezistenta de iesire va fi:

![]() (15)

(15)

Curentul injectat in tranzistoarele de intrare:

![]() (16)

(16)

Transconductanta tranzistoarelor de intrare :

![]() (17)

(17)

Nota: se foloseste notatia "N" la acesti parametri deoarece este vorba de tranzistoare NMOS; prin analogie, se va folosi notatia P pentru parametrii tranzistoarelor PMOS.

Din ecuatiile 15 si 17 rezulta expresia transconductantei de forma:

![]() (18) si

(18) si

![]() (19)

(19)

Timpul de intarziere va putea fi scris pe baza

relatiilor 14, 15, 16 si 19, iar relatia 20 arata ca acesta este dependent de parametrii

tranzistoarelor (![]() ,

,![]() ,

,![]() ) si de tensiunea de swing. Din moment ce stim

parametrii tranzistoarelor, nu ramane decat sa alegem o tensiune de swing atat

de extinsa cat ne permite tensiunea de prag a tranzistoarelor NMOS.

) si de tensiunea de swing. Din moment ce stim

parametrii tranzistoarelor, nu ramane decat sa alegem o tensiune de swing atat

de extinsa cat ne permite tensiunea de prag a tranzistoarelor NMOS.

![]() (20)

(20)

Pasul 3. Alegerea curentului de polarizare- ![]()

Se observa caCurentul de polarizare nu afecteaza timpul de intarziere; valoarea sa se stabili practic, prin simulare.

Pasul 4. Alegerea rezistentelor de sarcina- ![]()

In cazul Bufferului/Inversor, tensiunea pe aceste rezistente este:

![]() (21)

(21)

, iar curentul:

![]() (22)

(22)

Rezulta ca rezistentele vor fi exprimate de relatia:

![]() (23)

(23)

Pasul 5. Geometria tranzistoarelor de intrare

Latimea si lungimea tranzistoarelor NMOS de intrare se pot determina dupa urmatoarea relatie 24, iar valorile exacte vor fi stabilite practic, prin simulare.

(24)

(24)

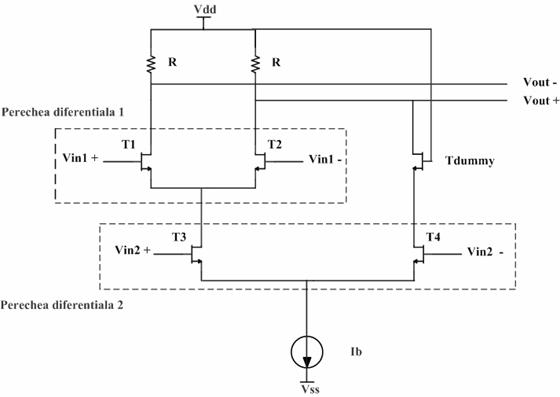

Poarta SI-NU

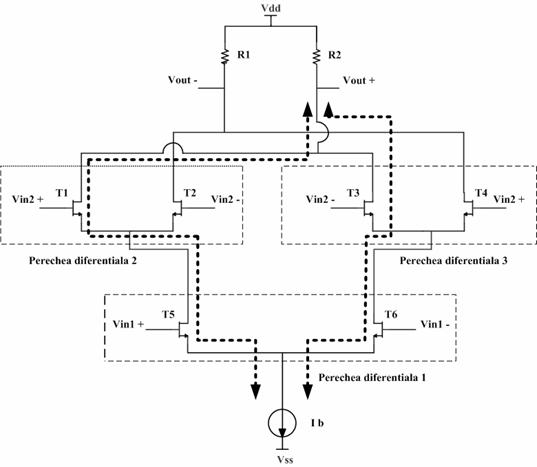

In figura 14 este

prezentata structura unei porti logice SI-NU cu doua intrari, Vin 1 si Vin 2.

Aceasta se obtine din Buffer/Inversor adaugand o pereche diferentiala, a carui

curent este controlat de cea de-a doua intrare V2. Perechea diferentiala conectata direct la

iesire e in regiunea saturata. Se va utiliza un tranzistor Tdummy in regim de

saturare, cu scopul de a asigura conditii similare pentru tranzistorul T3,

respectiv tranzistorul T4 , adica a echilibra valorile tensiunilor prin cele

doua cai, iar tensiunile ![]() sa fie egale pentru a

asigura simetria in tensiune a ramurilor etajului diferential.

sa fie egale pentru a

asigura simetria in tensiune a ramurilor etajului diferential.

Figura 14. Poarta SI-NU a familiei SCL

Pentru a determina tensiunea

de iesire se urmaresc aceeasi pasi descrisi la Buffer/Inversor, de la 1 la 5,

dar in plus va fi nevoie sa cunoastem dimensionarea tranzistoarelor din

perechea 2 care este polarizata in regim nesaturat (perechea de tranzistoare

T3, T4). Se va folosi notatia "![]() " pentru a face referire la perechea doi.

" pentru a face referire la perechea doi.

Pasul 6 Parametrii tranzistoarelor din perechea nesaturata

Pentru a putea comuta in

totalitate curentul de polarizare trebuie ca excursia tensiunii de intrare sa

asigure o comutatie completa care are loc daca prin poarta trece o tensiune pozitiva, iar tensiunea poarta-sursa

(gate-source)a tranzistorului este definita de relatia 25, unde ![]() - componenta continua:

- componenta continua:

![]() (25)

(25)

Celalalt tranzistor va fi complet inchis, de acea trebui ca valoarea tensiunii poarta-sursa sa fie:

![]() (26)

(26)

Din relatiile 25 si 26 rezulta ca tensiunea diferentiala de iesire a perechii 2 este:

![]() (27)

(27)

Datorita faptului ca excursia tensiunii de intrare este egala cu excursia tensiunii de iesire, este valabila si relatia:

![]() (28)

(28)

Dimensionarea trazistoarelor din perecehea 2 se va face dupa formula:

(29)

(29)

Cu ajutorul

structurii din figura 14, se pot obtine si celelate porti, Si, Sau/Sau-Nu, daca

modificam nivelele logice de la cele doua intrari, ![]() , respectiv

, respectiv ![]() .

.

Poarta XOR

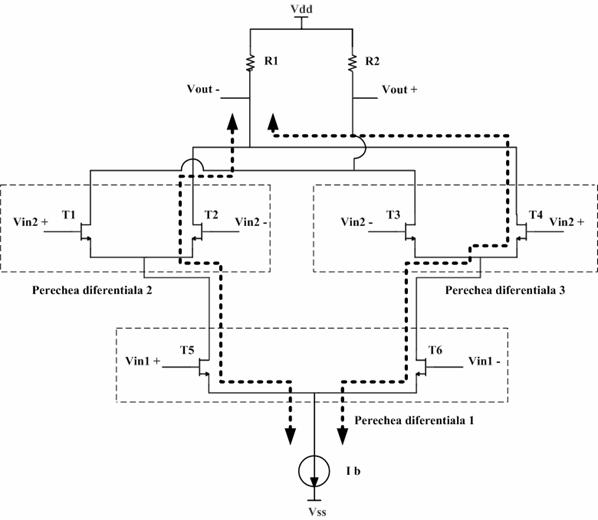

Operatia logica indeplinita

de poarta XOR este acea de a determina nivelul semnalului in starea High

simultan cu un al doilea semnal care se afla in starea Low. In figura 15 se va

examina poarta XOR cu doua intrari ![]() si

si ![]() . Din acest considerent rezulta ca este nevoie de doua nivele

de perechi diferentiale, nivelul 1 si nivelul 2 format din perechile

diferentiale 2 si 3, care au aceeasi tensiune de intrare (

. Din acest considerent rezulta ca este nevoie de doua nivele

de perechi diferentiale, nivelul 1 si nivelul 2 format din perechile

diferentiale 2 si 3, care au aceeasi tensiune de intrare (![]() ). [1]

). [1]

Figura 15. Poarta XOR SCL

In figura 15, am evidentiat

traseul pentru care iesirea ![]() se afla in stare Low iar iesirea

se afla in stare Low iar iesirea ![]() se afla in stare High.

Intrarea

se afla in stare High.

Intrarea ![]() se afla in starea Low, deci curentul din perechea

diferentiala 1 va trece prin tranzistorul

se afla in starea Low, deci curentul din perechea

diferentiala 1 va trece prin tranzistorul ![]() (se presupune ca

exista comutare totala de curent), deci, prin

(se presupune ca

exista comutare totala de curent), deci, prin ![]() nu circula deloc

curent, si perechea diferentiala 2 este ignorata complet. Intrarea

nu circula deloc

curent, si perechea diferentiala 2 este ignorata complet. Intrarea ![]() se afla deasemenea in starea Low, in acest caz curentul din

perechea diferentiala 3 va trece prin tranzistorul

se afla deasemenea in starea Low, in acest caz curentul din

perechea diferentiala 3 va trece prin tranzistorul ![]() si prin rezistenta

si prin rezistenta ![]() , si va exista o cadere de tensiune pe

, si va exista o cadere de tensiune pe ![]() .

.

Din aceste considerente putem descrie traseul prin relatiile:

![]()

(30)

(30)

Tot pentru a se obtine starea

Low la iesirea ![]() si starea High la iesirea

si starea High la iesirea ![]() , se va urma celalalt traseul descris tot in figura 15.

Intrarea

, se va urma celalalt traseul descris tot in figura 15.

Intrarea ![]() se afla in starea High, deci curentul din perechea diferentiala

1 va trece prin tranzistorul

se afla in starea High, deci curentul din perechea diferentiala

1 va trece prin tranzistorul ![]() (se presupune ca

exista comutare totala de curent), adica prin

(se presupune ca

exista comutare totala de curent), adica prin ![]() nu circula deloc

curent, perechea diferentiala 3 va fi complet ignorata. Intrarea

nu circula deloc

curent, perechea diferentiala 3 va fi complet ignorata. Intrarea ![]() se afla tot in starea

High, curentul va trece prin tranzistorul

se afla tot in starea

High, curentul va trece prin tranzistorul ![]() , iar iesirea

, iar iesirea ![]() va fi in starea logica

Low.

va fi in starea logica

Low.

![]()

(31)

(31)

Prin analogie se pot descrie si celelalte doua trasee ale portii logice XOR, evidentiate in figura de mai jos. Calcularea parametrilor tranzistoarelor si a tensiunilor se va face urmarind pasii descrisi la Buffer/Inversor si poarta logica Si/Si-Nu

Figura 16. Poarta XOR SCL

Figura 16 prezinta celelalte doua cai ale curentului ,

pentru care semnalul de la iesire se afla in stare High. Calea din dreapta este

pentru intrarea ![]() in stare Low, si

atunci curentul trece prin tranzistorul

in stare Low, si

atunci curentul trece prin tranzistorul ![]() , prin perechea diferentiala 2 nu va circula curent si

intrarea

, prin perechea diferentiala 2 nu va circula curent si

intrarea ![]() se afla in stare High.

Calea din stanga fiind pentru

se afla in stare High.

Calea din stanga fiind pentru ![]() in stare High, curentul va trece prin

in stare High, curentul va trece prin ![]() , prin perechea diferentiala 3 nu va circula curent, iar intrarea

, prin perechea diferentiala 3 nu va circula curent, iar intrarea

![]() va fi in stare Low.

va fi in stare Low.

SCL Latch

Circuitul Latch sau elementul de stocare, reprezinta un bloc foarte important utilizat in circuitele logice secventiale, cum ar fi bistabilul Flip-Flop, despre care se va vorbi in subpunctul urmator al lucrarii. Are doua functii esentiale, de a stoca valoarea semnalului pentru un timp specificat, iar cealalta de a genera nivele logice cu ajutorul buclei pozitive de reactie (feedback).

Figura 16. Circuitul Latch

In figura 16 se va observa

schema circuitului Latch. Se utilizeaza o pereche de tranzistoare NMOS, ![]() si

si ![]() care au grilele si

drenele legate incrucisat (drena tranzistorului

care au grilele si

drenele legate incrucisat (drena tranzistorului ![]() este legata la poarta tranzistorului

este legata la poarta tranzistorului ![]() , respectiv drena tranzistorului

, respectiv drena tranzistorului ![]() este legata la sursa tranzistorului

este legata la sursa tranzistorului ![]() ). Se observa doar doua terminale care sunt utilizate si ca

intrari si ca iesiri. Daca se aplica o aumita tensiune de intrare latch-ului

). Se observa doar doua terminale care sunt utilizate si ca

intrari si ca iesiri. Daca se aplica o aumita tensiune de intrare latch-ului ![]() , iar la un moment dat se decupleaza de la acea sursa de

tensiune de intrare, in acel moment circuitul va putea detecta semnul tensiunii

si va regenera nivelul logic corespunzator intrarii respective.

, iar la un moment dat se decupleaza de la acea sursa de

tensiune de intrare, in acel moment circuitul va putea detecta semnul tensiunii

si va regenera nivelul logic corespunzator intrarii respective.

De exemplu, daca va detecta o

tensiune intre ![]() si

si ![]() ca fiind pozitiva,

latch-ul va duce nivelul tensiunii

ca fiind pozitiva,

latch-ul va duce nivelul tensiunii ![]() catre nivelul logic

High si nivelul tensiunii

catre nivelul logic

High si nivelul tensiunii ![]() catre nivelul logic

Low , pana cand diferenta dintre acestea va fi egala cu o excursie a tensiunii data,

catre nivelul logic

Low , pana cand diferenta dintre acestea va fi egala cu o excursie a tensiunii data,

![]() . In momentul in care aceste nivele logice sunt sesizate,

latch-ul va memora valorile tensiunilor de la terminalele sale si le va mentine

constante. Astfel se va putea cupla ulterior un circuit care sa citeasca si sa

folosesca valorile

. In momentul in care aceste nivele logice sunt sesizate,

latch-ul va memora valorile tensiunilor de la terminalele sale si le va mentine

constante. Astfel se va putea cupla ulterior un circuit care sa citeasca si sa

folosesca valorile ![]() , respectiv

, respectiv ![]() .

.

Valorile tensiunilor de iesire si dimensionarea tranzistoarelor se va face utilizand aceleasi relatii ca si la Bufferul/Inversor.

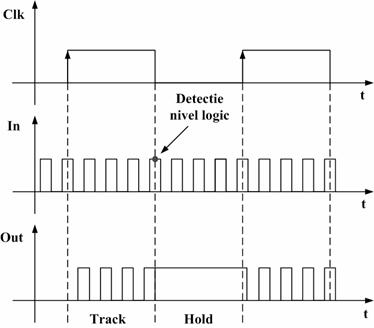

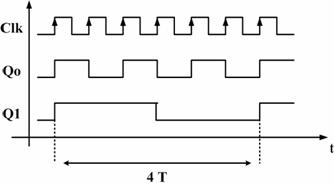

Pentru a prezenta mai in

detaliu functia Latch-ului, urmarim figura 17, in care este prezentat semnalul

de ![]() , activ pe palierul pozitiv, semnalul de intrare

, activ pe palierul pozitiv, semnalul de intrare ![]() , si semnalul de iesire

, si semnalul de iesire ![]() ; atat timp cat semnalul de Clock este in stare High, iesirea

va transmite exact ce vede la intrare, insa atunci cand se comuta in starea

Low, Latch-ul va citi nivelul de semnal care il vede la intrare, va decide daca

este High sau Low si va mentine acest nivel pana la urmatoare comutare a

Clock-ului.

; atat timp cat semnalul de Clock este in stare High, iesirea

va transmite exact ce vede la intrare, insa atunci cand se comuta in starea

Low, Latch-ul va citi nivelul de semnal care il vede la intrare, va decide daca

este High sau Low si va mentine acest nivel pana la urmatoare comutare a

Clock-ului.

Figura 17. Evidentierea functiilor circuitului Latch

D Latch

Circuitul D-Latch poate fi obtinut prin combinarea unei porti logice si a unui circuuit Latch, ambele controlate de o pereche diferentiala de tranzistoare cu rol de a comuta curentul, fie prin circuitul portii logice, fie prin Latch. Poarta logica poate fi un Buffer/Inversor, Si/Si-Nu, Sau/Sau-Nu, etc.

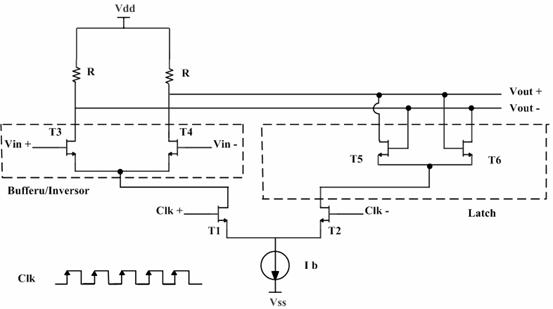

In figura de mai jos am exemplificat D Latch-ul

implementat cu ajutorul unui inversor, format din tranzistoarele ![]() si

si ![]() , a unui Latch, format din tranzistoarele

, a unui Latch, format din tranzistoarele![]() si

si ![]() , si a unei porti diferentiale formata din tranzistoarele

, si a unei porti diferentiale formata din tranzistoarele ![]() , respectiv

, respectiv ![]() . Curentul prin circuit este dirijat de semnalul de intrare

. Curentul prin circuit este dirijat de semnalul de intrare ![]() si semnalul

si semnalul ![]() . Acesta din urma, are ca rol sa comute curentul fie prin

Buffer/Inversor, fie prin Latch, cu ajutorul perechii diferentiale

. Acesta din urma, are ca rol sa comute curentul fie prin

Buffer/Inversor, fie prin Latch, cu ajutorul perechii diferentiale ![]() -

-![]() .

.

Se pot considera doua cazuri

de functionare, primul, cand semnalul de clock este activat de fronturile

crescatoare iar al doilea , cand este activat de fronturile descrescatoare. Prin

circuitul inversor, semnalul de intrare va injecta fie rezistenta ![]() , fie rezistenta

, fie rezistenta ![]() , iar Latch-ul va fi capabil sa regenereze nivelul logic si

sa se comporte si ca un element de stocare a acestuia.

, iar Latch-ul va fi capabil sa regenereze nivelul logic si

sa se comporte si ca un element de stocare a acestuia.

Figura 17. Poarta D-Latch

De exemplu, daca nivelul logic al semanlului de clock se afla in starea logica High (in figura starea High e considerata ca fiind activata de fronturile crescatoare a semnalului de clock), va functiona Bufferul/Inversor. Pe masura ce are loc comutare semnalului de clock in starea Low, Bufferul/Inversor va fi decuplat, nu va mai functiona, in timp ce nivelul logic de la iesirea lui va fi regenerat si apoi stocat (memorat) de catre Latch.

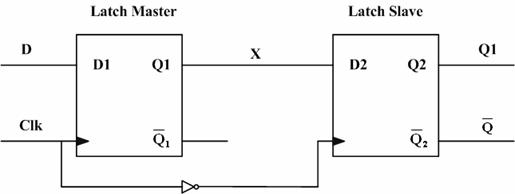

D Flip-Flop (DFF)

D Flip-Flop este un circuit care se utilizeaza cu precadere in detectoarele de faza, fiind folosit pentru a modifica momentul de declansare a unui semnal (retime data signal) dar si ca divizor de frecventa.

Acesta este compus din doua circuite D Latch conectate in configuratia Master / Slave, in asa mod in care este ilustrat in figura 18.

Figura 18. Master-Slave Flip Flop

Cand nivelul logic al semnalului de clock se afla in starea logica High, Latch-ul Master va procesa valoarea semnalului de intrare, in functie de poarta logica cu care este implementat, iar latch-ul slave va functiona ca un buffer, adica va retine valoare respectiva. Fiecare din circuitele D Latch va avea in componenta sa un element care va efectua o operatie logica (Inversor, AND/NAND, OR/XOR, etc).

Deci, fiecare D Latch va functiona dupa regula: cand semnalul de clock se afla in starea logica High, va fi activa poarta logica din interiorul acestuia, iar cand semnalul de clock se afla in starea logica Low, va fi activata functia de buffer implementata de Latch. Se va folosi un inversor pentru a insera semnalul de clock negat in Latch-ul Slave, fata de Latch-ul Master. Asadar, al doilea Latch va actiona ca un element de stocare, pentru ca semnalul de clock la intrarea lui se afla in starea logica Low.

Divizor cu 4

Acest circuit este un exemplu de circuit prin care se poate face divizarea frecventei. El poate fi realizat prin conectarea in cascada a doua circuite de divizare cu 2.

Figura 19. Starile logice ale intarilor

Daca la intrare sunt conectate semnalele ![]() , respectiv

, respectiv ![]() , putem urmari in figura19 starile logice.

, putem urmari in figura19 starile logice.

Figura 20. Divizare cu 4

In figura 20 observam ca semnalul de intrare![]() , comuta nivelul semnalului din starea High in starea Low,

dupa 4 perioade de tact, iar semnalul de intrare

, comuta nivelul semnalului din starea High in starea Low,

dupa 4 perioade de tact, iar semnalul de intrare ![]() , comuta nivelul semnalului din starea High in Low dupa doua

perioade de tact. Mai multe detalii de implementare a divizorului cu 4 vor fi

descrise in capitolul 4.

, comuta nivelul semnalului din starea High in Low dupa doua

perioade de tact. Mai multe detalii de implementare a divizorului cu 4 vor fi

descrise in capitolul 4.

|

Politica de confidentialitate |

| Copyright ©

2025 - Toate drepturile rezervate. Toate documentele au caracter informativ cu scop educational. |

Personaje din literatura |

| Baltagul caracterizarea personajelor |

| Caracterizare Alexandru Lapusneanul |

| Caracterizarea lui Gavilescu |

| Caracterizarea personajelor negative din basmul |

Tehnica si mecanica |

| Cuplaje - definitii. notatii. exemple. repere istorice. |

| Actionare macara |

| Reprezentarea si cotarea filetelor |

Geografie |

| Turismul pe terra |

| Vulcanii Și mediul |

| Padurile pe terra si industrializarea lemnului |

| Termeni si conditii |

| Contact |

| Creeaza si tu |