Aceasta sectiune din manual contine urmatoarele subiecte:

1. Introducere

2. Registrul de control

3. Functionare

4. Intreruperea TMR0

5. Utilizarea timerului 0 cu un clock extern

6. Prescalerul TMR0

1.Introducere

Modulul Timer0 are urmatoarele trasaturi:

- 8-bit timer/counter

- poate fi scris si citit

- are un prescaler pe biti programabil software

- sursa de clock selectabila : externa sau interna

- generator de intrerupere la de pasire de la FFh la 00h

- selectarea frontului pentru clock-ul extern

Nota:

Pentru a realiza o asignare de prescalerului a regisrului TMR0, asignati pescalerul Watchdog Timer-ului

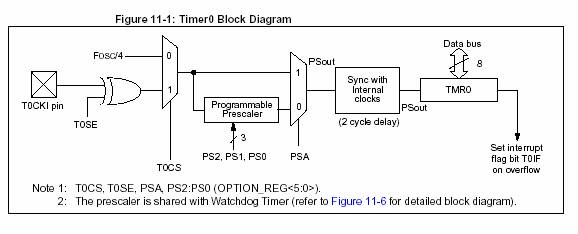

Figura 1 arata o diagrama simplificata a modulului Timer0

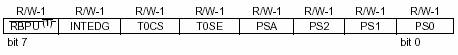

2.Registrul de control

Registrul OPTION_REG este un registru care poate fi scris sau citit care contine diferiti biti de control pentru configurarea prescalerului TMR0/WDT, intreruperii externe INT, TMR0, si micile pull-up-uride pe PORTB.

Nota:

Pentru a realiza o asignare de prescalerului a regisrului TMR0, asignati pescalerul Watchdog Timer-ului

Registrul OPTION_REG :

bit 7 RBPU(1) : bit de activare a Pull-up-urilor

1 =Pull-up-urile sunt dezactivate

0 =Pull-up-urile sunt activate prin valori inscrise in latch-urile porturilor individuale

bit 6 INTEDG : bitul de selectie a frontului intreruperii

1 = Intrerupere pe frontul crescator al pinului INT

0 = Intrerupere pe frontul descrescator al pinului INT

bit 5 T0CS : Bitul de selectie al sursei de clock pentru TMR0

1 = Tranzitie pe pinul T0CKI

0 = Clock-ul ciclului instructiunii interne (CLKOUT)

bit 4 T0SE : Bitul de selectie al frontului sursei TMR0

1 = Incrementare la tranzitia high-to-low a pinului T0CKI

0 = Incrementare la tranzitia low-to-high a pinului T0CKI

bit 3 PSA : bitul de asignare a prescalerului

1 = Prescalerul este asignat WDT-ului

0 = Prescalerul este asignat modulului Timer0

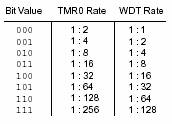

bit 2:0 PS2:PS0 :bitii de selectie a ratei prescalerului

Legenda

R = bit ce poate fi scris

W = bit ce poate fi scris

U = bit neimplementat, citi ca '0'

- n = valoare la reset POR

Nota 1:

Unele dispozitive numesc acest bit GPPU. Dispozitivele care au bitul RBPU, au pull-upuri slabe pe PORTB, in timp ce dispozitivele care au GPPU au pull-upuri slabe pe portul GPIO.

3. Functionare

Modul de lucru al Timerului este selectat prin resetarea bitului T0CS (OPTION<5>). In modul timer, modulul Timer0 va incrementa orice ciclu instructiune (fara prescaler). Daca registrul TMR0 este scris, incrementarea este inhibata pentru urmatoarele doua cicluri instructiune (figurile 11-2 si 11-3). Utilizatorul poate modifica acest lucru scriind o anume valoare in registrul TMR0. modul de numarare este selectat setand bitul T0CS (OPTION <5>). In modul contor, Timer0 va incrementa fie la fiecare front crescator sau descrescator al pinului T0CKI. Frontul pe care se incrementeaza este determinat de catre bitul de selectie al frontului sursei bitul T0SE(OPTION <4>). Resetand acest bit selecteaza frontul crescator. Restrictiile pe intrarea de clock extern sunt discutate in detaliu in sectiunea 5. Utilizarea timerului 0 cu un clock extern.

Prescalerul este de obicei impartit exclusiv intre modulul Timer0 si WatchdogTimer. Asignarea prescalerului este controlata prin software cu ajutorul bitului de control PSA (OPTION <3>). Resetand bitul PSA asignam prescalerul modulului Timer0. Prescalerul nu poate fi citit sau scris. Daca prescalerul este asignat modulului Timer0, valorile de prescalare de 1:2 ,,1:256 sunt selectabile. Sectiunea 6. Prescalerul TMR0 detaliaza operarea cu prescalerul.

Any write to the TMR0 register will cause a 2 instruction cycle (2TCY) inhibit. That is, after the

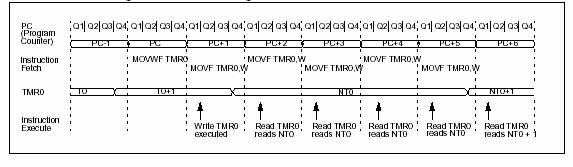

Orice scriere in registrul Timer0 va cauza o inhibare de 2 cicli instructiune (2TCY). Asta dupa ce registrul TMR0 a fost scris cu noua valoare, TMR0 nu va mai fi incrementat pana la al treilea ciclu instructiune (figura 2). Cand prescalerul este asignat modulului Timer0, orice scriere in registrul TMR0 va updata registrul TMR0 si reseta prescalerul. Incrementarea lui Timer0 (TMR0 si prescaler ) va fi inhibata deasemenea pentru 2 cicli instructiune (TCY). Astfel daca prescalerul este configurat ca 2, atunci dupa o scriere in registrul TMR0, Tmr0 nu va mai incrementa pentru 4 clok-uri ale lui Timer0 (figura 3). Dupa aceasta, TMR0 va incrementa orice numar de clock-uri ale prescalerului.

Figura 2 : Diagrama de semnal pentru Timer0 : Clock-ul intern/fara prescalare

Figura 3 Diagrama de semnal pentru Timer0 : Clock-ul intern/prescalare

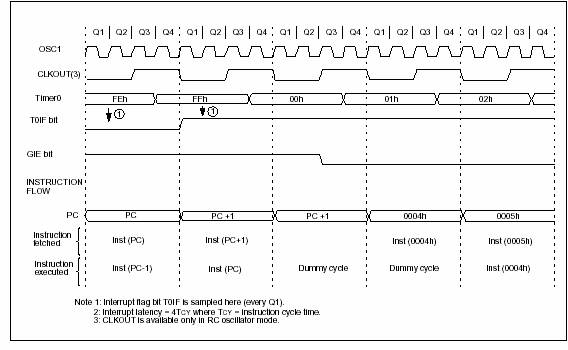

4. Intreruperea TMR0

Intreruperea este generata cand registrul TMR0 depaseste de la FFh la 00h. Aceasta depasire seteaza bitul T0IF (INTCON <2>). Intreruperea poate fi mascata resetand bitul T0IE (INTCON<5>). Bitul T0IF trebuie resetat software de catre rutina de tratare a intreruperii modulului Timer0 inainte de reactivarea acestei intreruperi. Intreruperea TMR0 nu poate trezi procesorul din SLEEP deoarece timerul este oprit in timpul perioadei de SLEEP. Vezi figura 4 pentru diagrama de semnal a intreruperii de Timer0.

Figura 4 : Diagrama de semnal pentru intreruperea Timer0

5. Utilizarea timerului 0 cu un clock extern

Cand este folosita o sursa de clock externa pentru Timer0, trebuie sa intalneasca anumite cerinte cum sunt detaliate in 5.1 'Sincronizarea cu Clock-ul Extern.' Aceste cerinte asigura faptul ca clock-ul extern este sincronizat cu clock-ul intern (TOSC). Deasemenea, este un delay in incementarea actuala a Timer0 dupa sincronizare.

5.1. Sincronizarea clock-ului extern

Cand prescalerul este folosit, intrarea de clock externa este aceeasi cu iesirea prescalerului. Sincronizarea lui T0CKI cu clock-ul intern este realizata prin esantionarea iesirea prescalerului in timpul ciclurilor Q2 si Q4 ale clock-ului intern (figura 5). Deci, este necesar penru T0CKI sa fie HIGH pentru cel putin 2TOSC (si un delay mic de 20ns date de un RC ) si LOW pentru cel putin 2TOSC (si un delay mic de 20ns date de un RC ).

Cand este folosit un prescaler ,intrarea de clock extern ese divizata de un prescaler de tip numarator de tranzitii asincrone astfel ca iesirea prescalerului este simetrica. Pentru ca clock-ul extern sa indeplineasca cerintele de esantionare, numaratorul trebuie luat in consideratie. prin urmare, este necesar ca T0CKI sa aiba o perioada de cel putin 4TOSC (si un delay mic de 40ns date de un RC) divizata de de catre valoarea prescalerului. Singura cerinta legata de durata palierelor de HIGH si LOW este ca ele sa nu incalce minimul duratei de puls de 10ns.

5.2. Delay-ul de incrementare al lui TMR0

Atat timp cat iesirea prescalerului este sincronizata cu clock-urile interne, este un delay mic din momentul in care frontul clock-ului extern apare pana in momentul in care modulul Timer0 este practic incrementat. Figura 5 arata acest delay.

Figura 5 : Diagrama de semnal pentru Timer0 cu clock extern

6. Prescalerul TMR0

Un registru numarator pe 8 biti este disponibil ca prescaler pentru modulul Timer0, sau ca postscaler pentru WatchdogTimer (figura 6). Pentru simplitate acest contor este referit ca 'prescaler' in descrierea timerului 0. Astfel, o asignare a prescalerului pentru modulul Timer0 inseamna ca nu exista postscaler pentru WatchdogTimer, si vice-versa.Bitii PSA si PS2:PS0 (OPTION <3:0>) determina asignarea prescalerului si ratia de prescalare. Cand este asignat modulului Timer0, toate instructiunile care scriu registrul Timer0 (ex. CLRF TMR0, MOVWF TMR0, BSF TMR0,x etc.) vor reseta prescalerul. Cand este asignat WatchdogTimerului, o instructiune CLRWDT va reseta prescalerul si WatchdogTimerul. Prescalerul nu poate fi citit sau scris.

Nota:

Exista un singur prescaler care este reciproc impartit exclusiv intre modulul Timer0 si WatchdogTimer.

Figura Diagrama bloc a prescalerului TMR0/WDT

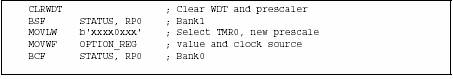

6.1. Schimbarea asignarii prescalerului

Asignarea prescalerului este in totalitate sub control software, ea poate fi schimbata pe loc in timpul executarii programului.

In exemplul 1, prima modificare a registrului OPTION_REG nu trebui neaparat inclusa daca prescalrea dorita este diferita de 1:1. Daca prescalarea finala este 1:1, atunci o valoare temporara de prescalare este setata (alta decat 1:1), si valoarea finala de prescalare este setata in ultima modificare a OPTION_REG.

Nota:

Penru a ocoli o restare nedorita a dispozitivului, uratoarea secventa de instructiuni (aratata in exemplul 1) trebuie executata and se schimba asignarea de la Timer0 la WDT. Aceasta secventa trebuie urmata chiar daca WDT este dezactivat.

Exemplul 1 : Schimbarea asignarii (Timer0 - WDT)

Pentru a schimba asignarea prescalerului de la WDT la modulul Timer0 folositi secventa aratata in exemplul 2.

Exemplul 2 : Schimbarea asignarii ( WDT-Timer0)

6.2. Initializarea

Cum Timer0 are o sursa de clock programabila, sunt doua exemple pentru a arata initializarea Timer0 cu fiecare sursa. Exemplul 3 arata initializarea pentru sursa interna de clock (modul timer), iar exemplul 4 arata initializarea folosind sursa de clock externa (modul numarator de evenimente).

Exemplul 3 : Initializarea lui Timer0 (cu sursa interna de clock)

Exemplul 4 : Initializarea lui Timer0 (cu sursa externa de clock)

|

Politica de confidentialitate |

| Copyright ©

2026 - Toate drepturile rezervate. Toate documentele au caracter informativ cu scop educational. |

Personaje din literatura |

| Baltagul caracterizarea personajelor |

| Caracterizare Alexandru Lapusneanul |

| Caracterizarea lui Gavilescu |

| Caracterizarea personajelor negative din basmul |

Tehnica si mecanica |

| Cuplaje - definitii. notatii. exemple. repere istorice. |

| Actionare macara |

| Reprezentarea si cotarea filetelor |

Geografie |

| Turismul pe terra |

| Vulcanii Și mediul |

| Padurile pe terra si industrializarea lemnului |

| Termeni si conditii |

| Contact |

| Creeaza si tu |